Acqua, servizi igienico-sanitari e andamento delle malattie a Patiya Upazila, Chittagong

Sajal Chandra Debnath; Shahriar Rahman; MD Touhiduzzaman

Etsi kirjoja tekijän nimen, kirjan nimen tai ISBN:n perusteella.

1000 tulosta hakusanalla Chandra A Clements

Sajal Chandra Debnath; Shahriar Rahman; MD Touhiduzzaman

Mohd Ziauddin Jahangir; P Chandra Shekar

Manjari Chandra

Lieberman Alicia; Compton Nancy C.; Horn Patricia van; Ippen Chandra Ghosh

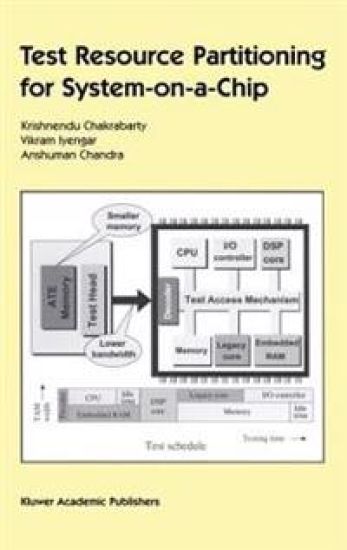

Vikram Iyengar; Anshuman Chandra

Vikram Iyengar; Anshuman Chandra

Lekkala Sivarama Prasad; Chandra Sekhar Akila; Ramachandra Reddy Arjula

Babita Kumari; Narinder Singh Atri; Ramesh Chandra Upadhyay

A Ramababu; Morusu Siva Sankar; N Sreeramulu

Atul; G. Divya Deepak; Madhab Chandra Behera

Rajeev Ranjan; Subhas Chandra Moi

P Dinakara Prasad Reddy; J N Chandra Sekhar; Ch Devi Sree

S. V. Jagadeesh Chandra; Mallem Kumar; V. V. Ramana

Kunal Sah; Janardhana Amaranath B J; Sunira Chandra

Annika Durve-Gupta; Naresh Chandra

![The Mutinies and the People, Or Statements of Native Fidelity, Exhibited During the Outbreak of 1857-58. by a Hindu [S.C. Mookerjee]](/covers/9781023842235.jpg)

Sambhu Chandra Mookerjee

![The Mutinies and the People, Or Statements of Native Fidelity, Exhibited During the Outbreak of 1857-58. by a Hindu [S.C. Mookerjee]](/covers/9781023846905.jpg)

Sambhu Chandra Mookerjee

P. T. Chandra